【學術論文】D類放大器pop-click噪聲抑制和飽和失真補償技術

摘要:

基於移動設備應用,在D類放大器設計中提出爆裂和咔嚓(pop-click)噪聲抑制及飽和失真補償技術。通過檢測電源電壓,順序控制前置放大器、功率級驅動電路,並在放大器輸出與地之間提供放電通道,有效減小爆裂和咔嚓噪聲幅度;在反饋環路結構D類功率放大器中,音頻輸入信號幅度過大,導致放大器輸出飽和失真,通過對脈衝寬度調製器輸出進行補償,可有效降低放大器的飽和失真,亦可消除因功率晶體管導通時間過長,而導致功率管發生熱損壞的風險。採用上述技術的D類功率放大器在0.35 μm CMOS工藝技術上實現,在電源電壓爲3.6 V時,放大器pop-click噪聲幅度爲2.0 mV,THD+N爲0.025%。

0 引言

在移動設備應用中,D類放大器與電池輸出直接連接成爲一種普遍的需求[1-2]。儘管已公開報道[1-2]無濾波D類放大器在效率以及動態範圍方面都具有良好的特性,但爆裂和咔嚓(pop-click)噪聲一直限制無濾波D類放大器在移動設備中的實際應用[3]。因此,與電池直接連接無濾波D類放大器設計中,抑制pop-click噪聲一直是設計難點。其次,應用於移動設備的D類功率放大器,系統結構常採用閉環結構以提高放大器性能,放大器的輸出(Vout)被反饋回來與輸入音頻信號進行疊加,形成閉環結構,反饋系統本身既能提高對電源和襯底噪聲的抑制能力,又能降低放大器的線性失真。然而,由於輸入信號與反饋信號通過積分器進行疊加,當輸入信號幅度較大時,積分器輸出容易飽和,而調製波形Vtri一般不能全電壓範圍調製,導致脈衝調製器調製失效,脈衝調製器輸出多個調製週期恆爲高電平或低電平。結果,D類放大器的功率開關經歷多個週期導通或關斷,輸出波形產生嚴重飽和失真,且極易造成功率器件因長時間導通而導致熱損壞。

根據上述設計需求,本文給出基於移動設備應用,在D類放大器設計中,提出能夠抑制pop-click噪聲的方法,以及減小積分器飽和失真的補償電路技術。文章首先給出pop-click噪聲產生的機理和抑制pop-click噪聲的具體電路實現方式,以及降低積分器飽和失真的具體電路實現方法,然後給出放大器的測試結果,最後進行總結。

1 電路設計

本設計提出的D類放大器系統框圖如圖1所示。主要由pop-click噪聲抑制電路、脈衝寬度調製(PWM)補償電路、前級放大器、積分器、振盪器和功率級等組成。本文主要就pop-click噪聲抑制電路和PWM補償電路進行詳細的討論。

1.1 pop-click噪聲抑制電路

pop-click噪聲的最大電平是音頻放大器性能重要指標,在放大器電源上電或去電時容易產生此噪聲,而人耳剛好對該噪聲敏感,儘可能減小或抑制放大器pop-click噪聲是D類放大器設計的關鍵。當放大器上電或去電時,D類放大器的pop-click噪聲產生主要來自兩個方面[3]:一是放大器的直流失調,另一個是PWM脈衝的突然開啓和關閉。放大器的直流失調電壓在開機時突然應用到放大器的輸出或者在關機時突然消失,PWM脈衝的突然產生或突然消失,在D類放大器的輸出端產生一個過渡階段,引起的pop-click噪聲電平開始很大,然後由於負反饋環路的抑制作用逐漸消失,這個過程儘管很短,但人耳仍然能夠聽到。爲避免人耳聽到這些噪聲,研究人員提供多種有效的措施。從公開的報道來看,有以下幾種技術:文獻[4]通過在音頻放大器的電源電壓管腳放置(RC)濾波電路或者採用模擬開關把直流電源接入放大器電源管腳,該方法由於不易集成,且會造成系統功耗和成本的額外消耗,應用場合受限;文獻[5]給出單端輸入音頻信號放大器的抑制pop-click噪聲的方法,該方法通過快速調整放大器輸入級共模電平以及在放大器的調製級引入虛擬開關爲建立偏置和反饋電壓/電流(BFVC)提供開關信號。文獻[3]通過引入可編程輔助驅動器反饋迴路來抑制pop-click噪聲,以及調整驅動器的驅動能力來開啓放大器的功率開關。上述兩種利用反饋技術抑制pop-click噪聲,由於反饋網絡存在環路調整過程,如果環路響應時間慢,對抑制pop-click噪聲效果較差,而環路響應太快,則易引起放大器環路不穩定;因此爲抑制pop-click噪聲,在放大器中引入反饋網絡會造成電路設計複雜以及功耗的增加,因此並不實用。綜合上述考慮,本文將給出一種簡單而實用的可單片集成抑制pop-click噪聲方式。

圖1中,爲消除D類放大器的前級放大器輸入失調電壓引起的pop-click噪聲,內部集成時序邏輯控制電路,工作過程如下:第一階段,電路上電過程中,如果電源電壓低於閾值電壓Vref1,芯片處於關斷階段,此時放大器的前置放大器、積分器、PWM調製器、功率開關均處於關閉階段,放大器無輸出。第二階段:外接耦合電容快速充電過程,當電源電壓高於閾值電壓Vref1,欠壓鎖定(UVLO)輸出高電平,開啓前置放大器中內部偏置電路,偏置電路快速給外接耦合電容充電,耦合電容上電壓快速達到共模電平(本設計爲VDD/2),爲避免在給外接電容充電過程中,放大器輸出端產生失調信號,開關S1,S2處於閉合狀態,前置放大器差分輸入爲0,同時放大器的反饋電阻R3、R4短路,因此,全差分放大器(FDA)的差分輸出爲零,電路如圖2所示。第三階段:耦合電容上共模電壓矯正階段,UVLO信號經過延遲時間(TD1),圖2中,開關S1關閉,S2保持開啓狀態,功率晶體管處於關閉輸出高阻狀態(揚聲器處於“安靜”狀態)。此時,音頻輸入信號進入放大器FDA1的輸入端,消除前置放大器輸入直流失調電壓,抑制PWM比較器產生咔嚓噪聲脈衝。第四階段:開啓功率級開關階段,S1關閉,S2關閉,前置放大器正常放大輸入音頻信號,前置放大器的輸出信號進入到積分器和PWM調製器進行調製。最後,S2通過時間延遲TD3後CTL_DRI變爲高電平,開啓PWM調製器以及功率開關,使輸出PWM波通過功率開關供給負載,整個芯片正常工作。該方法無反饋迴路,故不會影響放大器環路的穩定性。同理,在放大器電源電壓去電階段,芯片內部通過檢測電源電壓,當電源電壓低於閾值Vref2時,欠壓保護電路產生關斷信號,首先經過延遲時間TD4關閉前置放大器和積分器電路,積分器的輸出電壓逐漸減小(積分電容放電過程),PWM調製的輸出脈衝逐漸變窄,揚聲器輸出聲音逐漸消失,避免整個芯片瞬間關斷,揚聲器產生爆裂噪聲,圖3給出本設計時序圖。

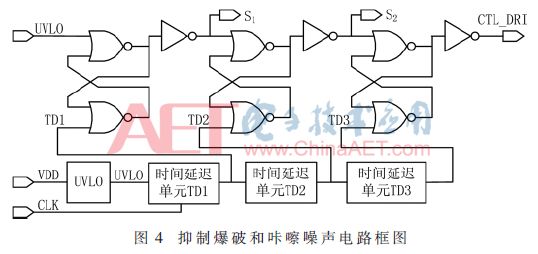

圖4給出抑制pop-click噪聲電路框圖,由UVLO電路模塊和數字時間延遲單元構成。其中UVLO電路模塊如圖5(a)所示,由電阻分壓電路,失調比較器,反相器鏈構成,其中電阻分壓電路採樣電源電壓,失調比較器產生遲滯閾值電壓,圖5(b)給出失調比較器電路圖,失調電壓由CTL和分別控制晶體管M5和M6使差分輸入對M1和M2不對稱生成,其失調電壓由電阻ROS大小決定。

1.2 PWM補償電路

在反饋結構D類功率放大器中,積分器用於對輸入音頻信號和反饋信號進行求和,如圖1所示,當輸入音頻信號幅度過大,積分器容易出現飽和,在多個時鐘週期內,脈衝寬度調製器輸出恆爲高電平或低電平。爲防止積分器輸出飽和,而導致功率開關MP1和MP2在多個開關週期常開或者常關,在脈衝調製器的輸出引入PWM補償電路,設置PWM脈衝的最大佔空比和最小佔空比,保證在一個時鐘週期以內,輸出功率器件開關一次,達到保護功率器件的目的,同時儘可能減小輸出波形飽和失真。PWM補償電路如圖6所示,由補償時鐘產生電路和PWM矯正邏輯電路構成。兩路補償時鐘(Vtri_PH1和Vtri_PH2)由圖7中電路產生。正常情況下,VPWM佔空比介於5%與95%之間,此時,VPWM_COR=VPWM,當 VPWM佔空比小於5%,VPWM_COR=Vtri_PH1,而當VPWM佔空比大於95%,VPWM_COR=Vtri_PH2。

圖7給出了三角波生成器電路結構[6],電路由兩個比較器、RS觸發器、充電放電路徑以及電阻分壓構成。該電路提供D類放大器的調製波形,同時產生用於PWM補償電路的補償信號Vtri_PH1以及Vtri_PH2。其工作原理如下:爲了能夠獲得三角波Vtri,採用恆定電流源IREF給電容CTRI充放電的模式,圖7中,第一比較器(COMP1)對輸入電壓Vtri與電壓VTH1進行比較,當Vtri>VTH1,比較器輸出爲高電平,圖中RS鎖存器的輸出被置位爲邏輯高電平,晶體管M1關閉,同時M2開啓,電容CTRI開始放電,當Vtri<VTH2,第二比較器COMP2輸出爲高電平,RS鎖存器輸出被複位爲邏輯低電平,晶體管M2關閉,M1開啓,電容CTRI開始衝電,由於IREF爲恆電流源,故CTRI上的電壓爲線性度良好的三角波,有利於減小放大器的諧波失真。

本設計中,VTH1和VTH2由電源電壓VDD採用比例電阻分壓獲得,可得到振盪器輸出頻率與電源電壓無關[6]。振盪器輸出波形如圖8所示。在本設計,典型輸入電壓爲3.6 V時,三角波頻率爲300 kHz,Vtri_PH1和Vtri_PH2佔空比設計均爲95%。

2 測試結果

基於CSMC 0.35 μm CMOS工藝設計D類音頻功率放大器,其版圖照片如圖9所示,單通道芯片面積爲0.85 mm2。本設計中,基於鋰電池移動設備應用,電源電壓範圍爲2.5~4.2 V,開關頻率爲300 kHz。圖10給出了電源電壓分別爲2.5 V、3.6 V、4.2 V,負載電阻爲8 Ω測試條件下,THD+N與輸出功率曲線。由圖中可得,當電源電壓爲3.6 V時,輸出功率約400 mW時,放大器的THD+N最小可到0.025%;表1給出本設計D類放大器部分測試結果。

3 結論

本文基於移動設備應用提出一種抑制pop-click噪聲電路技術,在電源上電和去電時通過時序電路控制放大器內部電路順序開啓和關斷,有效地減小pop-click噪聲幅度,噪聲幅度小於2.0 mV。通過對脈衝寬度調製信號進行脈衝補償,消除積分器飽和而造成功率開關晶體管損壞的風險,同時減小當輸入信號幅度太大引起的飽和失真。這些技術的引入,並沒有犧牲放大器的效率、THD+N以及輸出功率等性能。

參考文獻

[1] BERKHOUT M,DOOPER L.Class-D audio amplifiers in mobile applications[J].IEEE Transactions on Circuits & Systems I Regular paper,2010,57(5):992-1002.

[2] CHOI Y,TAK W,YOON Y,et al.A 0.018% THD+N,88 dB PSRR PWM Class-D amplifier for direct battery hookup[J].IEEE Journal of Solid-State Circuits,2012,47(2):454-463.

[3] JIANG X,SONG J,WANG M,et al.Integrated pop-click noise suppression,EMI reduction,and short-circuit detection for Class-D audio amplifiers[J].IEEE Journal of Solid-State Circuits,2013,48(4):1099-1108.

[4] Tim Lok.音頻Click和Pop噪聲的特性和消除技巧[J].工業和信息化教育,2010(8):61-65.

[5] Wang Haishi,Zhang Bo,Sun Jiang.Ways to suppress click and pop for class D amplifiers[J].Journal of Semiconductors,2012,33(8):1-5.

[6] ZHENG H,ZHU Z,MA R.A 0.02% THD and 80 dB PSRR filterless class D amplifier with direct lithium battery hookup in mobile application[J].Journal of Semiconductors,2017,38(7):56-63.

作者信息:

鄭 浩,劉延飛,王秋妍,楊晶晶,楊東東

(火箭軍工程大學,陝西 西安710025)