《自然》:人工智能提速計算機芯片設計速度超28倍

原標題:《自然》:人工智能提速計算機芯片設計速度超28倍

澎湃新聞見習記者 邵文

原本人類專家需要花費數週時間完成的芯片佈局設計,目前通過一種深度強化學習方法,平均6小時內就能完成這個過程,速度超28倍。

6月10日,來自美國加州谷歌研究院(Google Research)的Azalia Mirhoseini、Anna Goldie等在國際頂級學術期刊《科學》(Science)發表的一篇論文《一個快速芯片設計的布圖佈局方法》(A graph placement methodology for fast chip design)中指出,機器學習工具可以極大地加速計算機芯片設計。

Barrett et al.

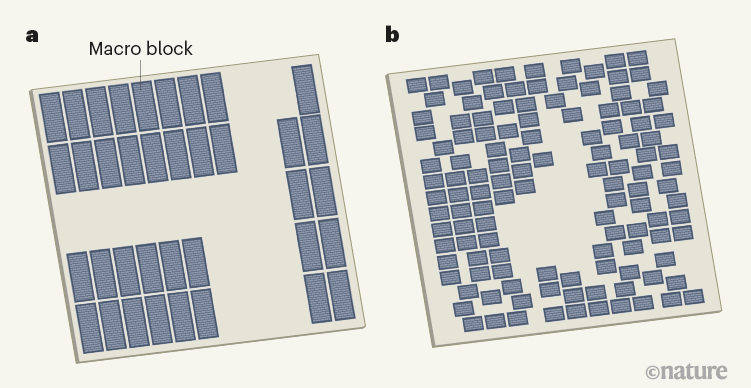

微芯片的面積約爲幾十到數百毫米平方,在一塊指甲蓋大小的硅片上排列並互連了數十億個晶體管。每個芯片可以包含數千萬個邏輯門,稱爲標準單元,以及數千個存儲塊,稱爲宏塊或宏。單元和宏塊通過數十公里的佈線互連以實現設計的功能。

芯片中單元和宏塊的位置對設計結果至關重要。它們的位置決定了佈線必須跨越的距離,從而影響能否在組件之間成功布線以及信號在邏輯門之間傳輸的速度。

美國加州大學聖迭戈分校的Andrew Kahng在《自然》發表的《人工智能系統在設計微芯片平面圖方面勝過人類》(AI system outperforms humans in designing floorplans for microchips)中寫道,微芯片設計的成敗在很大程度上取決於“佈局規劃” (floorplanning)和放置的步驟。

這些步驟決定了內存和邏輯元件在芯片上的位置,相應的位置會極大地影響芯片設計是否能夠滿足處理速度和電源效率等操作要求。到目前爲止,尤其是在佈局規劃方面沒有任何自動化嘗試。因此,它常常是由專業的人類工程師在數週或數月內反覆和艱苦地執行的。在芯片的設計過程中,全局佈線是最複雜和耗時的階段之一,也是決定芯片整體性能的關鍵。

谷歌的研究團隊發現,機器學習工具可以用來加速“佈局規劃”的流程。該研究團隊將芯片的佈局規劃部分設計爲一個強化學習問題,並開發了可完成可行芯片設計的神經網絡。他們訓練了一個強化學習智能體,這個智能體會把佈局規劃看作一個棋盤遊戲:元件是“棋子”,放置元件的畫布是“棋盤”,“獲勝結果”則是根據一系列評估指標評出的最優性能(評估基於一個包含1萬例芯片佈局的參考數據集)。

作者指出,這種方法能在6小時內設計出與人類專家不相上下或是更好的可行芯片佈局。

人類設計的微芯片平面圖與機器學習系統生成的平面圖不同

Andrew Kahng認爲,“開發出比當前方法更好、更快、更省錢的自動化芯片設計方法,有助於延續芯片技術的‘摩爾定律’ 。”摩爾定律指每塊芯片的元件數量大約每兩年會翻一番,這種進步速度相當於芯片上組件數量每週增加約1%。“因此,無法自動進行佈局規劃是有問題的——不僅因爲相關的時間成本,還因爲它限制了芯片開發計劃中可以探索的解決方案的數量。”

他還表示,研究團隊的佈局規劃方案已經被應用在谷歌的下一代AI處理器的設計上,這也顯示出其可應用於大規模生產。除了加速芯片設計外,該研究或也能用於優化城市規劃、疫苗測試等。