我國學者首次實現具有亞1納米柵極長度的晶體管

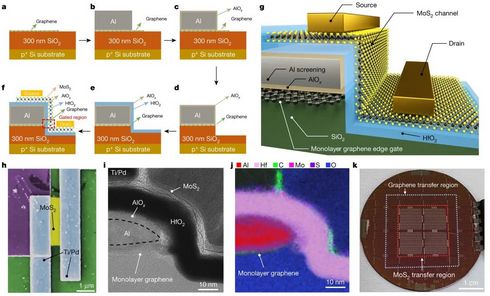

亞1納米柵長晶體管器件工藝流程示意圖、表徵圖以及實物圖 清華大學供圖

晶體管是芯片的核心元器件。更小的柵極尺寸可以使得芯片上集成更多的晶體管,並帶來性能上的提升。近日,清華大學集成電路學院教授任天令團隊在小尺寸晶體管研究方面取得重要進展,首次實現了具有亞1納米柵極長度的晶體管,該晶體管具有良好的電學性能。相關成果以“具有亞1納米柵極長度的垂直硫化鉬晶體管”爲題,在線發表在《自然》上。

1965年,英特爾公司創始人之一的戈登·摩爾提出:“集成電路芯片上可容納的晶體管數目,每隔18-24個月便會增加一倍,微處理器的性能提高一倍,或價格下降一半。”該論斷也被稱爲“摩爾定律”。過去幾十年,晶體管的柵極尺寸在摩爾定律的推動下不斷微縮,然而近年來,隨着晶體管的物理尺寸進入納米尺度,電子遷移率降低、漏電流增大、靜態功耗增大等短溝道效應越來越嚴重,這使得新結構和新材料的開發迫在眉睫。

根據國際器件和系統路線圖(IRDS2021)報道,目前主流工業界晶體管的柵極尺寸在12納米以上,如何促進晶體管關鍵尺寸的進一步微縮,引起了業界研究人員的廣泛關注。

在極短柵長晶體管方面,學術界此前也做出了很多探索。2012年,日本產業技術綜合研究所在國際電子器件大會報道了基於絕緣襯底上硅實現V形的平面無結型硅基晶體管,等效的物理柵長僅爲3納米。

2016年,美國的勞倫斯伯克利國家實驗室和斯坦福大學在《科學》期刊報道了基於金屬性碳納米管材料實現了物理柵長爲1納米的平面硫化鉬晶體管。

爲進一步突破1納米以下柵長晶體管的瓶頸,任天令研究團隊利用石墨烯薄膜超薄的單原子層厚度和優異的導電性能作爲柵極,通過石墨烯側向電場控制垂直的二硫化鉬(MoS2)溝道的開關,從而使等效的物理柵長度降爲0.34納米。再通過在石墨烯表面沉積金屬鋁並使其自然氧化,完成了對石墨烯垂直方向電場的屏蔽。此後,科研人員使用原子層沉積的二氧化鉿作爲柵極介質、化學氣相沉積的單層二維二硫化鉬作爲溝道,最終完成了具有亞1納米柵極長度的晶體管。

研究發現,相較於體硅材料,單層二維二硫化鉬具有更大的有效電子質量和更低的介電常數,在亞1納米物理柵長的控制下,晶體管能有效的開啓、關閉,其關態電流在pA量級。

基於工藝計算機輔助設計(TCAD)的仿真結果進一步表明,石墨烯邊緣電場對垂直二硫化鉬溝道的有效調控,預測了在同時縮短溝道長度條件下,晶體管的電學性能情況。研究人員表示,這項工作推動了摩爾定律進一步發展到亞1納米級別,同時爲二維薄膜在未來集成電路的應用提供了參考依據。

相關論文鏈接:https://doi.org/10.1038/s41586-021-04323-3

來源:中國科學報