英特爾“續命”摩爾定律,稱2030年實現萬億級晶體管芯片設計

記者/彭新

半導體長年按照大約2年性能翻倍的“摩爾定律”進化。其原動力是減小晶體管等的尺寸,以提高集成度的微細化技術。近年對於“摩爾定律”可行性的爭論在半導體業界時有發生,但半導體大廠英特爾仍是摩爾定律的堅定支持者。

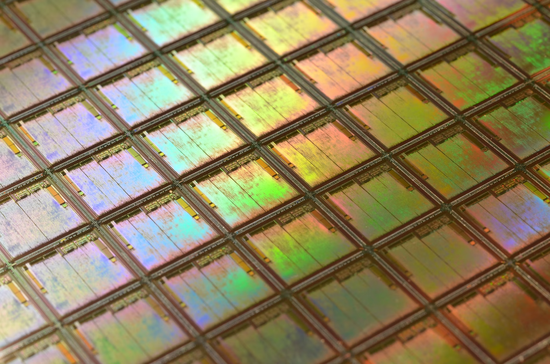

本週,在半導體行業會議IEDM 2022(2022年IEEE國際電子器件會議)上,英特爾發佈多篇論文,包括2D材料、3D封裝技術、存儲器技術等多項技術進展。該公司還表示,將在未來十年內持續推進摩爾定律,預計到2030年可實現在單個封裝中集成一萬億個晶體管。

“目前我們可以在單個封裝放入1千億個晶體管,還有10倍需要增加。”12月8日,英特爾中國研究院院長宋繼強在接受界面新聞等採訪中稱,他表示,從2023年到2030年,晶體管密度要在8年時間裏翻10倍,即實現2的3次方的提升,是一個比較激進的目標。

同時,目前半導體晶體管結構正從FinFET(鰭式場效應晶體管)向GAAFET(環繞柵極晶體管)架構發展,相較於目前先進製程所採用的FinFET(鰭式場效應晶體管),GAAFET架構有着更好的靜電特性,在尺寸相同的情況下,可以達到更高的頻率,功耗也更低,因此是當前3納米等高端工藝的核心技術。宋繼強指出,在GAAFET架構下進一步微縮,會出現漏電流及不易控制通斷等問題,用傳統的硅材料去做通道材料面臨諸多挑戰。

宋繼強稱,要達到單個封裝中集成一萬億個晶體管的目標,一方面要繼續依靠晶體管微縮,例如用超薄的2D材料做更高效的GAA的晶體管。另一方面還需要依賴3D封裝技術,能夠進一步提升整個設備中的晶體管總量。

兩大方向英特爾在IEDM發表的論文中均有涉及,英特爾介紹,新材料和工藝模糊了封裝和芯片製造之間的界限,與2021年公佈的成果相比,通過混合鍵合技術將互連間距繼續微縮到3微米,密度又提升了10倍。同時通過超薄“2D”材料即過渡金屬硫化物,可以在單個芯片上集成更多晶體管。

過去,英特爾在先進製程技術研究中大多傾向於“單打獨鬥”,自行攻克所有難關,隨着英特爾近年在先進製程競爭中落後於臺積電,已經逐步改變做法。宋繼強以先進封裝技術應用爲例稱,先進封裝可以把不同的芯粒(Chiplet)集成,涉及到芯片中不同芯粒的互聯互通時,則需要設計廠商、晶圓廠和封裝廠、EDA工具廠商共同協作,在協議層面做好規範,此外軟件工具也需要升級改造以支持芯粒設計。

負責技術開發的英特爾副總裁安Ann Kelleher在本週表示,公司完全走在正軌上,英特爾目前設有季度里程碑,從這些里程碑看,公司提前或處於正軌上。她表示,英特爾正採取比過去更加務實做法,建立應急計劃以確保不再出現重大延遲。同時,公司也更多地依賴設備供貨商的幫助,而不是試圖自己做所有的工作。

按照英特爾規劃的進度,該公司目前正在進行Intel 4(即7納米)工藝生產,預計年底就會進入試產階段,未來將用於第14代的Meteor Lake處理器架構,並且已經準備好在2023下半年邁入Intel 3(3納米)製程技術,外界普遍認爲第一批產品會在2024上半年登場。